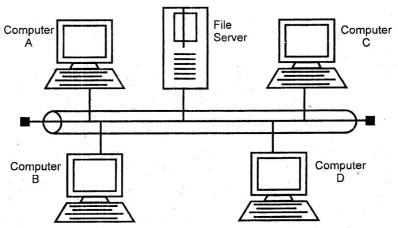

#### **Hubs:** (c)

- (1)In some network topologies, mostly ARCNET based star topologies, a device hub is used.

- Hub is a connecting device in which cables can be connected without soldering wires to centralise (2)network traffic through a single connecting point.

### There are three types:

(1)Active hub (2) Passive hub (3) Switching hub

Active hub: interconnect the network and also amplifies the signal received apart from splitting and retransmitting it to the destination.

**Passive hub**: It only splits and transmits signal received and it can not amplify it. This do not contian any electronic component.

**Switching hub**: This quickly routes the signals between ports of hubs. It can be used in place of router.

#### 2. (A)

- $(1/, \times 6 \text{ pts} = 3)$ **(a)** Microprocess 8085 has 8-bit data bus and 16-bit address bus. (1)

- The least significant 8-bits of address bus are passed on the same eight lines as that of data bus i.e. (2)on the signal lines  $AD_7 - AD_0$ .

- (3) These signal lines are bi-directional.

- They are used for dual purpose for lower order 8-bit of address and as well as 8-bit of data. This (4) is known as multiplexing and such bus is known as multiplexed bus.

- In multiplexed means, first to select one and then other. (5)

- In executing an instruction, during earlier part of cycle these lines are used as the lower order (6)address bus. During label part of cycle, these lines are used as data bus.

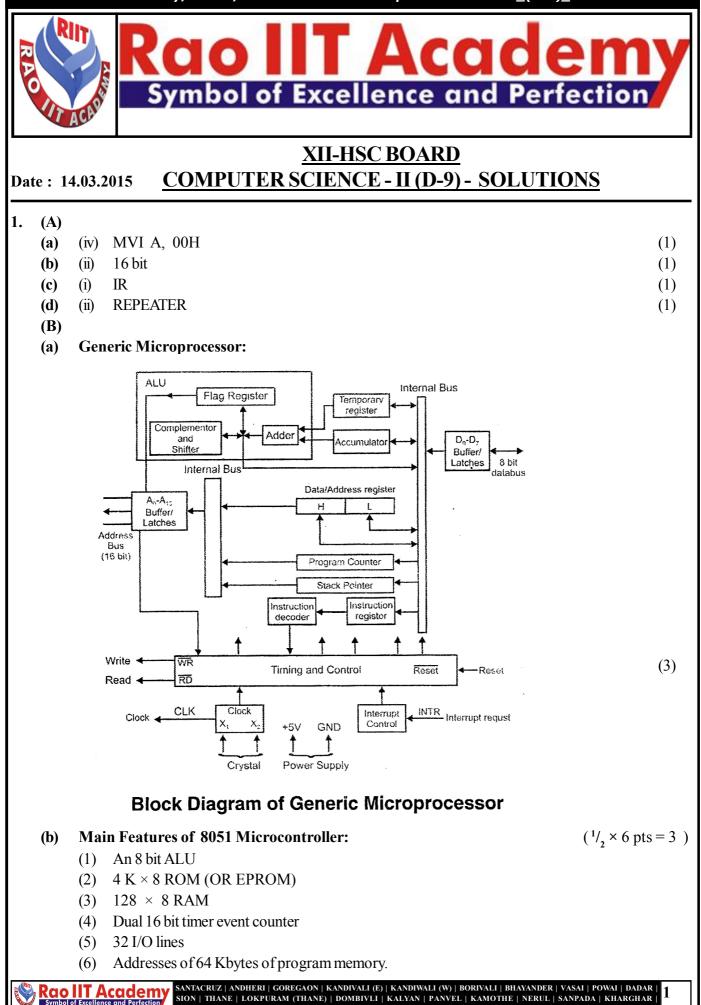

#### **(b) BUS Topology :**

- (1) In a BUS physical topology, all the devices are connected to a common shared cable, called as backbone of the network.

- (2) A BUS physical topology is shown in following figure :

The bus is available for each node to send its data to each and every computer node. (3)

KANDIVALI (E) | KANDIWALI (W) | BORIVALI | BHAYA Rao IIT Academy SION | THANE | LOKPURAM (THANE) | DOMBIVLI | KALYAN | PANVEL | KAMOTHE | NERUL | SANPADA | KHARGHAR

(1)

(2)

$(1^{1}/,)$

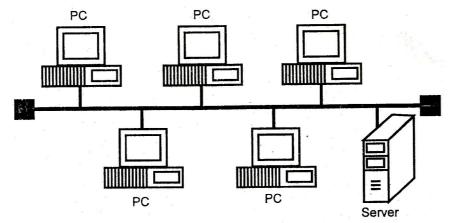

## **STAR Topology:**

- (1) In a STAR topology all the workstations are connected to central hub.

- (2) The hub receives signal from a workstation and routes it to the proper destination.

- (3) STAR physical topology is often implemented to implement BUS or RING logical topology.

$(1 \frac{1}{2})$

(4) A STAR topology is shown in following figure:

Rao IIT Academy Symbol of Excellence and Perfection Symbol of Excellence and Perfection

|                                   | Rao II                               | IT Academy/ 2015 / XII-HSC - Board -Computer Science - II_(D-9)_SOLUTION                       | S                 |  |  |

|-----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------|-------------------|--|--|

|                                   | Log                                  | gical Instructions :                                                                           | $(1 \frac{1}{2})$ |  |  |

|                                   | (1)                                  | ANA r : [LOGICALAND WITH ACCUMULATOR]                                                          |                   |  |  |

|                                   |                                      | Format : $[A] \leftarrow [A] \land [r]$                                                        |                   |  |  |

|                                   |                                      | Addressing : Register addressing                                                               |                   |  |  |

|                                   |                                      | Group : Logical group                                                                          |                   |  |  |

|                                   |                                      | Bytes : 1 byte                                                                                 |                   |  |  |

|                                   |                                      | Flag : S, Z, P are modified $Cy = 0$ , $Ac = 1$                                                |                   |  |  |

|                                   | (2)                                  | ANI data : [ADD IMMEDIATE WITH ACCUMULATOR]                                                    |                   |  |  |

|                                   |                                      | Format : $[A] \leftarrow [A] \land data$                                                       |                   |  |  |

| Addressing : Immediate addressing |                                      |                                                                                                |                   |  |  |

|                                   |                                      | Group : Logical group                                                                          |                   |  |  |

|                                   |                                      | Bytes : 2 bytes                                                                                |                   |  |  |

|                                   |                                      | Flag : S, Z, P are modified $Cy = 0$ , $Ac = 1$                                                |                   |  |  |

|                                   | (3) ORA M : [LOGICAL OR WITH MEMORY] |                                                                                                |                   |  |  |

|                                   |                                      | Format : $[A] \leftarrow [A] \lor [[H] [L]]$                                                   |                   |  |  |

|                                   |                                      | Addressing : Register Indirect                                                                 |                   |  |  |

|                                   |                                      | Group : Logical group                                                                          |                   |  |  |

|                                   |                                      | Bytes : 1 byte                                                                                 |                   |  |  |

| <b>(D)</b>                        |                                      | Flag : S, Z, P are modified Ac and Cy are rest                                                 |                   |  |  |

| (B)                               | (1)                                  | 8085 provides 5 hordware interrupts:                                                           | (1)               |  |  |

| <b>(a)</b>                        | (1)                                  |                                                                                                | (1)               |  |  |

|                                   |                                      | (i) TRAP (ii) RST 7.5 (ii) RST 6.5 (iv) RST 5.5 (v) INTR                                       |                   |  |  |

|                                   | (2)                                  | These interrupts are vectored interrupts. It means that when these interrupts are given, it is | directed          |  |  |

|                                   |                                      | (or vectored) to transfer the control to specific memory location given by                     |                   |  |  |

|                                   |                                      | $TRAP = 4.5 \times 8 = 0024 H \qquad RST \ 7.5 = 7.5 \times 8 = 003 C H$                       |                   |  |  |

|                                   |                                      | RST $6.5 = 6.5 \times 8 = 0034$ H RST $5.5 = 5.5 \times 8 = 002$ C H                           |                   |  |  |

|                                   | (3)                                  | Among these interrupts, TRAP is non-maskable interrupt which can not be disabled. But          | the other         |  |  |

|                                   |                                      | four interrupts are maskable interrupts, which can be disabled.                                |                   |  |  |

|                                   | (4)                                  | The TRAP has highest priority and the INTR has lowest priority among the hardware in           | terrupts.         |  |  |

|                                   |                                      | The hardware interrupts in descending order of priority are listed below:                      |                   |  |  |

|                                   |                                      | (i) TRAP - highest priority (ii) RST 7.5                                                       |                   |  |  |

|                                   |                                      | (iii) RST 6.5 (iv) RST 5.5                                                                     |                   |  |  |

|                                   |                                      | (v) INTR - lowest priority.                                                                    | (3)               |  |  |

|                                   |                                      |                                                                                                | × /               |  |  |

|                                   |                                      |                                                                                                |                   |  |  |

|    | F             | Rao Il         | T Academy/ 2                  | 015,              | / XII-HSC - Board -Computer Science - II_(D-9)_SOLUTION                                                                                                                                | S            |

|----|---------------|----------------|-------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|    | <b>(b)</b>    | (i)            | MOV B, M                      | :                 | [MOVE FROM MEMORY]                                                                                                                                                                     | (1)          |

|    |               |                | Format                        | :                 | $[B] \leftarrow [[H] - [L]]$                                                                                                                                                           |              |

|    |               |                | Addressing                    | :                 | Register Indirect addressing                                                                                                                                                           |              |

|    |               |                | Group                         | :                 | Data transfer group                                                                                                                                                                    |              |

|    |               |                | Bytes                         | :                 | 1 byte                                                                                                                                                                                 |              |

|    |               |                | Flag                          | :                 | None                                                                                                                                                                                   |              |

|    |               | (ii)           | ADC C                         | :                 | [ADD REGISTER TO ACCUMULATOR WITH CARRY]                                                                                                                                               | (1)          |

|    |               |                | Format                        | :                 | $[A] \leftarrow [A] + [C] + [Cy]$                                                                                                                                                      |              |

|    |               |                | Addressing                    | :                 | Register addressing                                                                                                                                                                    |              |

|    |               |                | Group                         | :                 | Arithmetic group                                                                                                                                                                       |              |

|    |               |                | Bytes                         | :                 | 1 byte                                                                                                                                                                                 |              |

|    |               |                | Flag                          | :                 | All                                                                                                                                                                                    |              |

|    |               | (iii)          | SPHL                          | :                 | [MOVE HL TO SP]                                                                                                                                                                        | (1)          |

|    |               |                | Format                        | :                 | $[SP_L] \leftarrow [L]$                                                                                                                                                                |              |

|    |               |                |                               |                   | $[SP_H] \leftarrow [H]$                                                                                                                                                                |              |

|    |               |                | Addressing                    | :                 | Register addressing                                                                                                                                                                    |              |

|    |               |                | Group                         | :                 | Machine control group [stack operation]                                                                                                                                                |              |

|    |               |                | Bytes                         |                   | 1 byte                                                                                                                                                                                 |              |

|    |               |                | Flag                          |                   | None                                                                                                                                                                                   |              |

|    |               | (iv)           | XCHG: [EXC                    | СНА               | NGE H AND L WITH D AND E                                                                                                                                                               | (1)          |

|    |               |                | Format                        | :                 | $[H] \leftrightarrow [D]$                                                                                                                                                              |              |

|    |               |                |                               |                   | $[L] \leftrightarrow [E]$                                                                                                                                                              |              |

|    |               |                | Addressing                    | :                 | Register                                                                                                                                                                               |              |

|    |               |                | Group<br>Bytes                | •                 | Data transfer group<br>1 byte                                                                                                                                                          |              |

|    |               |                | Flag                          | :                 | None                                                                                                                                                                                   |              |

| 3. | (A)           |                |                               |                   |                                                                                                                                                                                        |              |

|    | <b>(a)</b>    | Mic            | rocontroller is a             | a Sin             | gle Chip Computer. This is used for dedicated functions.                                                                                                                               | (1)          |

|    |               |                | antages:                      |                   |                                                                                                                                                                                        | (2)          |

|    |               | (1)            |                               |                   | ependent controllers in various machines.                                                                                                                                              |              |

|    |               | (2)            |                               |                   | entials of a computer on a single chip like CPU, R/W memory, ROM                                                                                                                       | 1 It can be  |

|    |               | (2)            | used as a micro               | -                 |                                                                                                                                                                                        | larry a a st |

|    |               | (3)            | products like to              |                   | f a system than microprocessor based system. So it can be used in                                                                                                                      | low cost     |

|    | (h)           | (1)            | Dual Pipelinin                | 2                 |                                                                                                                                                                                        | (1)          |

|    | (b)           | (1)            | -                             | 0                 | lar architecture incorporates a dual-pipelining in Pentium processo                                                                                                                    | . /          |

|    |               |                | -                             |                   | ess more than one instruction per clock cycle and achieve a high                                                                                                                       |              |

|    |               |                |                               | proc              | less more than one instruction per clock cycle and achieve a high                                                                                                                      |              |

|    |               | $(\mathbf{n})$ | performance.<br>Branch Predic | tion              |                                                                                                                                                                                        | (1)          |

|    |               | (2)            |                               |                   |                                                                                                                                                                                        | (1)          |

|    |               |                |                               | U                 | of branch prediction is that, using it, the Pentium makes an educated instruction following a conditional instruction will be                                                          | guess        |

|    |               |                |                               |                   | instruction following a conditional instruction will be.                                                                                                                               |              |

| /  |               |                |                               |                   | e instruction cache from running dry during conditional instruction.                                                                                                                   |              |

| R  | Rao<br>Symbol | of Excellen    | cademy SANTAC                 | RUZ   AI<br>THANE | NDHERI   GOREGAON   KANDIVALI (E)   KANDIWALI (W)   BORIVALI   BHAYANDER   VASAI   POWAI   DAI<br>  LOKPURAM (THANE)   DOMBIVLI   KALYAN   PANVEL   KAMOTHE   NERUL   SANPADA   KHARGH | DAR   5      |

(3) On chip changes :

The data and code on-chip caches improves the processing speed of the Pentium processor.

- (4) 64-Bit Data Bus :

- (i) Pentium has 64 bit data bus which allows higher speed of data transfer to it.

- (ii) The data transfer speed of pentium is twice as fast as a processor with 32-bit data bus.

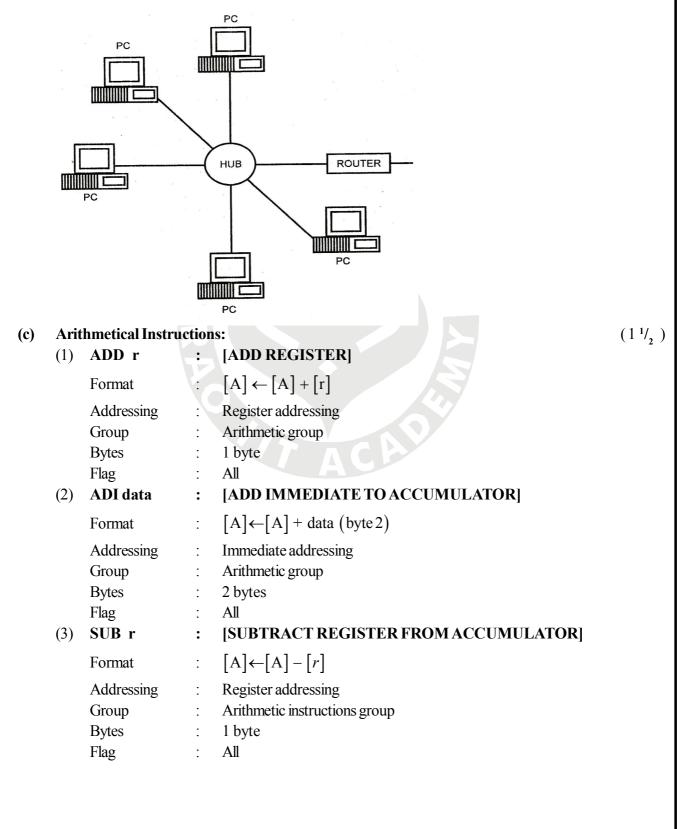

- (c) (1) Ethernet devices are connected to a common shared medium that provides the path along which the electronic signals will travel. Historically, this medium was co-axial cable. But now-a-days twisted pair cable or fibre optic cable are also used.

- (2) Ethernet network transmit data in small units called frames.

- (3) Each frame must contain source address as well as destination address, which identifies recepient and sender of message. The address will uniquely identify node. No two Ethernet devices can have same address.

- (4) Ethernet network is as shown in following figure.

In above figure when computer A sends message to computer C, computers B and D will also get the message and check whether the diestinations address matches to its own address or not, if not, it will discard the frame. (3)

(B) (a)

## PUSH-PUSH REGISTER PAIR ON STACK

(2)

This is a single byte instruction. The contents of the register pair specified in the operand are copied into the stack.

- (1) The stack pointer is decremented and the contents of higher order register in pair (such as B in BC pair, D in DE pair) are copied on stack.

- (2) The stack pointer is decremented again and contents of lower order register are copied on the stack. No flags are modified. Contents of register pair are unchanged.

Example: PUSH D Will push contents of DE pair Let D = 15 H & E = 23 HLet SP = 2300 HThen after executing PUSH D we will get following contents in SP and stack.

Symbol of Excellence and Perfection

7 SANTACRUZ | ANDHERI | GOREGAON | KANDIVALI (E) | KANDIWALI (W) | BORIVALI | BHAYANDER | VASAI | POWAI | DADAR SION | THANE | LOKPURAM (THANE) | DOMBIVLI | KALYAN | PANVEL | KAMOTHE | NERUL | SANPADA | KHARGHAR

(1)

| SP = 22 FE | STACK |                 |

|------------|-------|-----------------|

| 22 FE      | 23H   | $\leftarrow$ SP |

| 22FF       | 15H   |                 |

| 2300       |       |                 |

## POP-POP OFF STACK TO REGISTER PAIR

(2)

(1)

(1)

(1)

(1)

This is single byte instruction. On execution copies two top bytes on stack to designated register pair in operand.

- (1) Contents of top most location of stack called stack top are copied into lower register (such as C in BC etc) of the pair. The SP is incremented by 1.

- (2) Contents of the stack location pointed by SP are copied into higher register of the pair. The stack pointer SP is incremented by 1. No flags are affected. Contents of stack are unchanged.

Example:

Consider SP = 22FE H with following contents stored on stack.

On execution of instruction POP H the contents of H, L, SP will be as shown in figure.

| SP = 22 FE | STACK |   |

|------------|-------|---|

| 22FE       | 10H   | ← |

| 22FF       | 24H   |   |

| 2300       | ZI    |   |

| ••• |                   |       |                 |  |  |  |  |  |

|-----|-------------------|-------|-----------------|--|--|--|--|--|

|     | SP = 2300         | STACK |                 |  |  |  |  |  |

|     | 22FE              | 10H   |                 |  |  |  |  |  |

|     | 22FF              | 24H   |                 |  |  |  |  |  |

|     | 2300              |       | $\leftarrow$ SP |  |  |  |  |  |

|     | H = 24 H L = 10 H |       |                 |  |  |  |  |  |

|     | AFTER EXECUTION   |       |                 |  |  |  |  |  |

**BEFORE EXECUTION**

8085 has five flags. Sign flag, zero flag, Auxiliary carry flag, Parity flag and Carry flag. A 8-bit register is used to represent five flags as shown in following figure.

| D | 7 | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ D | <b>)</b> 0 | Bit number       |

|---|---|-------|-------|-------|-------|-------|---------|------------|------------------|

| S |   | Ζ     | Ι     | Ac    |       | Ρ     | - C     | Σу         | ——— Status flags |

Where S - Sign flag, Z- Zero flag, Ac-Auxiliary carry flag, P - Parity flag, Cy- Carry flag.

# (1) Sign flag (S) :

**(b)**

After the execution of arithmetic and logic operation, if the most signification of the result is 1, then the flag is set to 1 otherwise 0.

This flag is used with signed number. If MSB is 1, the number will be negative and if it is 0, the number will be positive.

# (2) Zero flag(Z):

After performing an arithmetic or logic operations, if the result is zero, then zero flag is set to 1, else it is reset. This flag is modified by the results in accumulator as well as in other registers.

# (3) Auxiliary carry flag(Ac) :

In an arithmetic operation, when carry is generated from bit  $D_3$  to  $D_4$ , the auxiliary carry flag is set to 1. This flag is only available internally and used for B.C.D. operations and not available for programmer.

# (4) Parity flag (P) :

Parity flag is set to 1, if the result stored in accumulator contains even parity, i.e., even number of 1's. If accumulator contains odd number of 1's, the flag is 0.

Rao IIT Academ

Y SANTACRUZ | ANDHERI | GOREGAON | KANDIVALI (E) | KANDIWALI (W) | BORIVALI | BHAYANDER | VASAI | POWAI | DADAR SION | THANE | LOKPURAM (THANE) | DOMBIVLI | KALYAN | PANVEL | KAMOTHE | NERUL | SANPADA | KHARGHAR

| <b>(a)</b>   | (i)                                                                    | INTA                                                                                                                                                                                           | (1             |  |  |  |  |  |

|--------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|

| ( <i>a</i> ) | (1)                                                                    | (1) $\overline{\text{INTA}}$ is an Abbrevation for interrupt acknowledgment.                                                                                                                   | (1             |  |  |  |  |  |

|              |                                                                        | (2) A low an $\overline{\text{INTA}}$ indicates that the processor has acknowledged an INTR interr                                                                                             | unt            |  |  |  |  |  |

|              | (ii)                                                                   | _                                                                                                                                                                                              |                |  |  |  |  |  |

|              | (ii)                                                                   | IO/M<br>(1) It is status signal indicates whether the address bus is far I/O device or far mana                                                                                                | (1             |  |  |  |  |  |

|              |                                                                        | (1) It is status signal indicates whether the address bus is for I/O device or for memo                                                                                                        | •              |  |  |  |  |  |

|              |                                                                        | (2) When it goes high, the address ont he address bus referring I/O device and when<br>the address on the address bus referring memory.                                                        | it goes i      |  |  |  |  |  |

|              | (iii)                                                                  | RD                                                                                                                                                                                             | (1             |  |  |  |  |  |

|              | ()                                                                     | (1) This is read control signal. This is active low signal.                                                                                                                                    | (-             |  |  |  |  |  |

|              |                                                                        | <ul><li>(2) This signal indicates that selected I/O or memory device is to be read and data is</li></ul>                                                                                       | availabl       |  |  |  |  |  |

| (b)          | (1)                                                                    | Microcontroller is a single chip microcomputer.                                                                                                                                                | w , while i    |  |  |  |  |  |

| (~)          | (1)                                                                    |                                                                                                                                                                                                |                |  |  |  |  |  |

|              | (3)                                                                    | They are used as independent controllers in machined or as slaves in distributed processing.<br>They are used as machine tools, chemical processors, medical instrumentation and sophisticated |                |  |  |  |  |  |

|              | (-)                                                                    | guidance control.                                                                                                                                                                              | - F            |  |  |  |  |  |

|              | (4)                                                                    | Some applications require simple timing and bit set/ reset functions; other require high speed data                                                                                            |                |  |  |  |  |  |

|              |                                                                        | processing capability.                                                                                                                                                                         |                |  |  |  |  |  |

|              | (5) Many low cost products such as electronic toys, microwave ovens, V |                                                                                                                                                                                                |                |  |  |  |  |  |

|              |                                                                        | microcontrollers.                                                                                                                                                                              |                |  |  |  |  |  |

|              | (6)                                                                    | A home security system, a tape deck and intelligent multimeter can also be built                                                                                                               | -              |  |  |  |  |  |

|              |                                                                        | -                                                                                                                                                                                              | 6  pts = 1     |  |  |  |  |  |

| (c)          |                                                                        | sted Pair Cable:                                                                                                                                                                               | $(1^{1}/_{2})$ |  |  |  |  |  |

|              | (1)                                                                    | It consists of a pair of wires or one or more pairs of two twiseted copper wires insula                                                                                                        | ation.         |  |  |  |  |  |

|              | (2)                                                                    | This is inexpensive medium.                                                                                                                                                                    |                |  |  |  |  |  |

|              | (3)                                                                    | EMI effect is maximum.                                                                                                                                                                         |                |  |  |  |  |  |

|              | Coa                                                                    | ixial Cable:                                                                                                                                                                                   | $(1^{1}/_{2})$ |  |  |  |  |  |

|              | (1)                                                                    | It is a hallow cable with a solid copper at the center of the cable surrounded by plast                                                                                                        | ic from.       |  |  |  |  |  |

|              | (2)                                                                    | Relatively expensive i.e. twice or thrice than twisted pair.                                                                                                                                   |                |  |  |  |  |  |

SANTACRUZ | ANDHERI | GOREGAON | KANDIVALI (E) | KANDIWALI (W) | BORIVALI | BHAYANDER | VASAI | POWAI | DADAR | SION | THANE | LOKPURAM (THANE) | DOMBIVLI | KALYAN | PANVEL | KAMOTHE | NERUL | SANPADA | KHARGHAR | 8 Rao IIT Academy Symbol of Excellence and Perfection

| F          | Rao II | IT Academy/ 2015 / XII-HSC - Board -Computer Science - II_(D-9)_SOLUTIONS                                                                                           |

|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>(B)</b> |        |                                                                                                                                                                     |

| <b>(a)</b> | (i)    | <b>T-States :</b> (1)                                                                                                                                               |

|            |        | The subdivision of an operation, which is performed in one clock period is called as T-state.                                                                       |

|            | (ii)   | Machine Cycle: (1)                                                                                                                                                  |

|            |        | Machine cycle is defined as the time required to complete any operation of accessing wither memory or I/O which is the subpart of an instruction.                   |

|            | (iii)  | Instruction Cycle: (1)                                                                                                                                              |

|            |        | An instruction cycle is defined as the time required to complete the execution of an instruction. The 8085 instruction cycle consists of one to five machine cycle. |

|            | (iv)   | FETCH Cycle : This question is out of syllabus so student will get bonus marks for this.                                                                            |

| <b>(b)</b> | (i)    | Fiber optic cable if cable is broke, still Data Transfer is possible, while in electrical cable its not possible.                                                   |

|            | (ii)   | In fiber optics cable, Data transfer is optically using light rays while in electrical cable, data transfer is done by electricity.                                 |

|            | (111)  | In fiber optic cable, data rate is very high in terms of gbps, while in electrical cable, its data rate is very low in terms of mbps.                               |

|            | (iv)   | Cost of fiber optic cable is very high while, in electric at cable its very low.                                                                                    |

(iv) Cost of fiber optic cable is very high while, in electric at cable its very low(4)

5. (a)

| Mnemonics    |    | Comment                             |  |  |

|--------------|----|-------------------------------------|--|--|

| Opcode Opera | nd | Comment                             |  |  |

| MVI A, 00    | )  | ; Store 00 to Acc                   |  |  |

| MOV D, A     | ł  | ; Store 00 to D Reg                 |  |  |

| LXI H, 80    | 85 | ; Reg 8085 in HL pair               |  |  |

| MOV B, N     | Л  | ; store content of Memory to B Reg  |  |  |

| MVI C, 09    | )  | ; Store count in C Register         |  |  |

| BACK: ADD B  |    | ; Addition of B reg with Acc.       |  |  |

| JNC : NE     | XT | ; Jump if Cy? 0, go to next         |  |  |

| INR D        |    | ; Increment D Reg. by 1             |  |  |

| NEXT: DCR C  |    | ; Decrement counter by 1            |  |  |

| JNZ : BA     | CK | ; Jump C? 0; go to Back             |  |  |

| INX H        |    | ; Increment HL pair by 1            |  |  |

| MOV M,       | A  | ; Result stored from Acc. to memory |  |  |

| INX H        |    | ; Increment HL pair by 1            |  |  |

| MOV M,       | D  | ; Store D reg to memory             |  |  |

| RST 1.0      |    | ; Restart.                          |  |  |

(5)

**(b)**

| Mnemonics             | Comment                          |  |  |

|-----------------------|----------------------------------|--|--|

| <b>Opcode Operand</b> | Comment                          |  |  |

| MOV A, E              | ; Copy E content to Accumulator  |  |  |

| СМА                   | ; Compliment Accumulator         |  |  |

| MOV L, A              | ; Copy Accumulator to L Register |  |  |

| MOV A, D              | ; Copy D content to Accumulator  |  |  |

| СМА                   | ; Compliment Accumulator         |  |  |

| MOV H, A              | ; Copy Acc. to HL Pair           |  |  |

| INX H                 | ; Increment HL pair by 1         |  |  |

| RST 1.0               | ; Restart.                       |  |  |

(c)

| Mne      | monics     | Commont                          |

|----------|------------|----------------------------------|

| Opcode   | Operand    | Comment                          |

| М        | VIC, 0A    | ; Block length in C Register     |

| L        | XI H, 2050 | ; Store 2050 in HL pair          |

| М        | IOV A, M   | ; Copy content of memory to Acc. |

| BACK: IN | VX H       | ; Increment HL pair by 1         |

| C        | CMP M      | ; Compare Acc. with memory       |

| J        | C : NEXT   | ; If $Cy = 1$ , then go to NEXT  |

| Ν        | MOV A, M   | ; Copy content of Memory to Acc. |

| NEXT : D | OCR C      | ; Decrement C Reg. by 1          |

| J        | NZ : BACK  | ; If Cy ? 0, then go to Back     |

| Γ        | NX H       | ; Increment HL by 1              |

| Ν        | AOV M, A   | ; Store Acc. content to memory   |

| R        | ST 1.0     | ; Restart.                       |

|          |            | OR A P                           |

(5)

(5)

(a)

| Mne      | monics      | Commont                         |  |

|----------|-------------|---------------------------------|--|

| Opcode   | Operand     | Comment                         |  |

| Ι        | .XI H, 8081 | ; Store 8081 in HL Pair.        |  |

| Ν        | AVI C, 14 H | ; Store count in C Register.    |  |

| Ν        | AVI A, BCH  | ; Store $BC_H$ in Accumulator . |  |

| BACK : N | MOV M, A    | ; Copy Acc content to memory.   |  |

| Ι        | NX H        | ; Increment HL pair by 1.       |  |

| Ι        | DCR C       | ; Decrement C Reg by 1.         |  |

| J        | NZ : BACK   | ; If C ? 0 then go to BACK.     |  |

| F        | RST 1.0     | ; Restart.                      |  |

(5)

## (b)

| Mnemonics             | Commont                        |

|-----------------------|--------------------------------|

| <b>Opcode Operand</b> | Comment                        |

| MVI C, 00             | ; Store 00 in C Register       |

| LXI H, 6067           | ; Store 6067 in HL pair        |

| MOV A, M              | ; Copy memory to Acc.          |

| INX H                 | ; Increment HL pair by 1       |

| MOV B, M              | ; Copy memory to B Register    |

| BACK: CMP B           | ; Compare Acc. with B Register |

| JC : NEXT             | ; If $Cy = 1$ , go to next     |

| SUB B                 | ; Subtract B from Acc.         |

| INR C                 | ; Increment C content by 1     |

| JMP : BACK            | ; Jump to Back                 |

| INX H                 | ; Increment HL pair by 1       |

| MOV M, C              | ; Store Quotient in memory     |

| INX H                 | ; Increment HL pair by 1       |

| MOV M, A              | ; Store Reminder in memory     |

| RST 1.0               | ; Restart.                     |

(5)

(c)

| Mnemonics                | Comment                      |  |

|--------------------------|------------------------------|--|

| <b>Opcode Operand</b>    | Comment                      |  |

| LIX H, 20F9 <sub>H</sub> | ; Store 20F9 in HL pair      |  |

| MOV A, M                 | ; Copy memory data to Acc.   |  |

| ANI OF                   | ; Logically And Acc. with 0F |  |

| MOV B, A                 | ; Copy Acc. to B Reg         |  |

| MOV A, M                 | ; Copy memory content to Acc |  |

| ANI F0                   | ; Logically And Acc. with F0 |  |

| RRC                      | ; Rotate digits              |  |

| CMP B                    | ; Compare Acc. with B reg.   |  |

| JNZ : NEXT               | ; If A? B; go to next        |  |

| MVI B, 00                | ; Store 00 in B reg.         |  |

| RST 1.0                  | ; Restart.                   |  |

| NEXT: MVI B, FF          | ; Store FF in B reg.         |  |

| RST 1.0                  | ; Restart.                   |  |

(5)